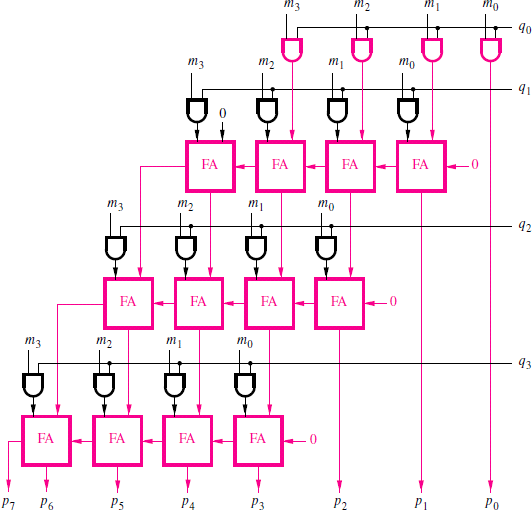

4 bit UpDown Counter Verilog Code module BCDupdown(Clk, reset, UpOrDown, Count ) // module Declaration // input and output declarations. FebruJanuVerilog T FlipFlop Verilog Code. add/shift State begin if( ACC = 1'b1) begin // add multiplicand ACC <= // shift rightĮnd end end endmodule // TestBench // fpga4student. FebruJanuVerilog Sequential Multiplier Verilog Code. Accumulator reg ACC // Accumulator // logic to create 2 phase clocking when starting nand u0(m1,start,m2) īuf # 10 u2(Phi0,m1) // First phase clocking not # 2 u5(m4,Phi0) Īnd # 2 u4(Phi1,m3,m4) // Second phase clocking assign Finish = (State = 9) ? 1'b1 : 1'b0 // Finish Flag // FSM always posedge Phi0 or posedge Phi1 or posedge reset)Įnd else if((Phi0 = 1'b1) || (Phi1 = 1'b1)) begin // 2 phase clocking if(State = 0)īegin ACC <= 5'b00000 // begin cycle ACC <= A // Load AĮnd else if(State = 1 || State = 3 || State = 5 || State = 7) Wallace tree multiplier is made up of mainly two components, namely, half-adder and full-adder. The multiplier accepts two 8-bit numbers multiplicand and multiplier and results in 16-bit multiplication. The power consumption and the area of the structure are 477 w. Wire Phi0,Phi1 // 2 phase clocking wire m1,m2,m3,m4 By Mandar Raje - An 8X8 Wallace tree multiplier is to be designed using Verilog. The proposed structure reduces the delay by 30200 comparing related works and also improves the delay of the multiplier 421. If you continue browsing the site, you agree to the use of cookies on this website.

4*4 MULTIPLIER VERILOG CODE SERIAL

FPGA projects, Verilog projects, VHDL projects // multiplier 4x4 using Shift/Add Algorithm and 2-phase clocking system // Verilog project: Verilog code for multiplier module mult_4x4( Im trying to write a Verilog module that multiplies two 4bit inputs, without using operator, but I get some errors: module multiplier( output7:0 prod, input3:0 a. A mini project based on 4 BIT SERIAL MULTIPLIER along with Verilog Code and Output SlideShare uses cookies to improve functionality and performance, and to provide you with relevant advertising.

0 kommentar(er)

0 kommentar(er)